# MULTI-STANDARD PRINTER BUFFER

Leycester Whewell's micro is quick off the mark thanks to this 256K printer buffer with Centronics and RS232

interfaces.

most irritating feature of many printers is their data acceptance rate. Many have sufficient capacity to hold only a single line of text, although some can store 2K, 4K or 8K of data. So, when listing a program or document of any reasonable size, the computer is effectively slowed down to the speed of the printer.

A printer buffer appears as a very fast printer to the computer, storing its output so that the operator can get on with the next task without an enforced coffee break. Meanwhile, the buffer outputs data to the printer at its normal speed.

## **Features**

Although the idea of a printer buffer is not a new one (and designs have appeared in ETI before) this device has an ample memory capacity of either 64K or 256K — approximately 20 or 80 pages of A4 text respectively.

The buffer also allows parallel-parallel, serial-parallel, parallel-serial and serial-serial data transfers with a serial data rate of either 1200 or 9600 baud. This should accommodate just about any combination of printer and micro.

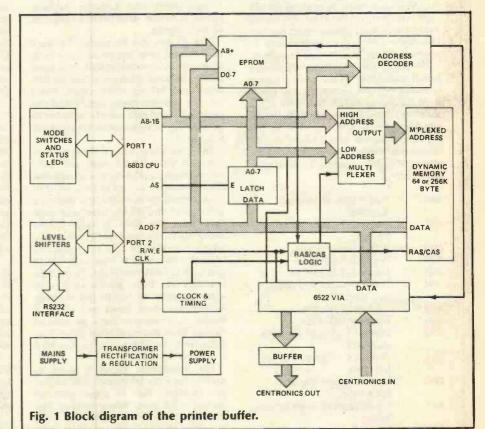

The unit is driven by an 8-bit microprocessor, the 6803 (see Fig. 1). This is a 6800 with the added features of 128 bytes of zero page RAM, a timer, a serial communications interface, parallel

I/O and some additional instructions.

Since the 6803 has only one serial interface, with I/O handshaking, one half is used to receive data and the other to transmit data. This combination prevents the use of XON and XOFF handshaking as an alternative to RTS and CTS. The same clock source drives both the receiver and transmitter, so serial-serial transfers must be at the

same baud rate.

A rotary switch selects the desired transfer combination with an eighth position reserved for a self test mode. This checks the memory and the parallel and serial interfaces. The status of each is indicated by flashing the LEDs on the front of the unit.

A PAUSE switch halts the output to the printer although data is still accepted from the host micro and the RESET switch resets the entire unit, clears any data present and allows a new operating mode to be selected.

Four LEDs indicate when the pause is active, when the buffer unit is empty of data and when the unit is full and the fourth flashes at about 1Hz with a duty cycle proportional to the fullness of the buffer memory.

The software checks the state

of the interfaces in turn in a continuous loop. Whenever a data transfer has been acknowledged then the next character is processed. This allows the asynchronous supply of data and retrieval of data from the buffer.

At the end of each loop the status LEDs are updated. A regular timed interrupt is used to initiate a software refresh of the DRAM and test whether the PAUSE switch is pressed or not.

# Construction

A soldering iron with a fine tip is needed to prevent solder bridges between the fine tracks of the PCB. Solder all the through pins first.

Unless you are an experienced constructor and have a temperature controlled iron, it is recommended that sockets are

# HOW IT WORKS

Whenever a microprocessor has to address more memory than it was originally intended for, there is always the problem of how to split it up. The buffer RAM is divided into 32K blocks—two for the 64K version and eight for the 256K version.

Three of the I/O lines on the 6803 (PI/O-2) act as extra address lines. The main difference between the 64K and 256K DRAM chips is that pin 1 is used for refreshing on the former and address line A8 on the latter. To prevent refresh cycles occuring on the 64K chips during a normal memory access cycle, the two I/O lines which are multiplexed to produce A8 are always kept at logic 1.

The paged DRAM is located between &4000 and &BFFF in the memory map with the EPROM occupying the space from &C000 to &FFFF. The only other memory mapped component, the 6522, is addressed at &100 to &10F in the partially decoded space below &4000. All the 6803's internal RAM, timer, serial and parallel data registers are located in page zero:

| &00    | Port 1 Data Direction      |

|--------|----------------------------|

|        | Register                   |

| &01    | Port 2 Data Direction      |

|        | Register                   |

| &02    | Port 1 Data Register       |

| &03    | Port 2 Data Register       |

| &04-07 | Unused, External Memory    |

| 808    | Timer Control and Status   |

|        | Register                   |

| &09    | Counter High Byte          |

| &0A    | Counter Low Byte           |

| &0B    | Output Compare Register    |

|        | High Byte                  |

| &0C    | Output Compare Register    |

|        | Low Byte                   |

| &0D    | Input Capture Register     |

|        | High Byte                  |

| &0E    | Input Capture Register Low |

|        | Byte                       |

| &0F    | Unused, Exernal Memory     |

| &10    | Rate and Mode Control      |

|        | Register                   |

| &11    | Transmit/Receive Control   |

|        | and Status Register        |

| &12    | Receive Serial Data        |

|        | Register                   |

| &10    | Transmit Serial Data       |

|        | Register                   |

| &14    | RAM Control Register       |

| &15-1F | Reserved                   |

| &20-7F | Unused, External Memory    |

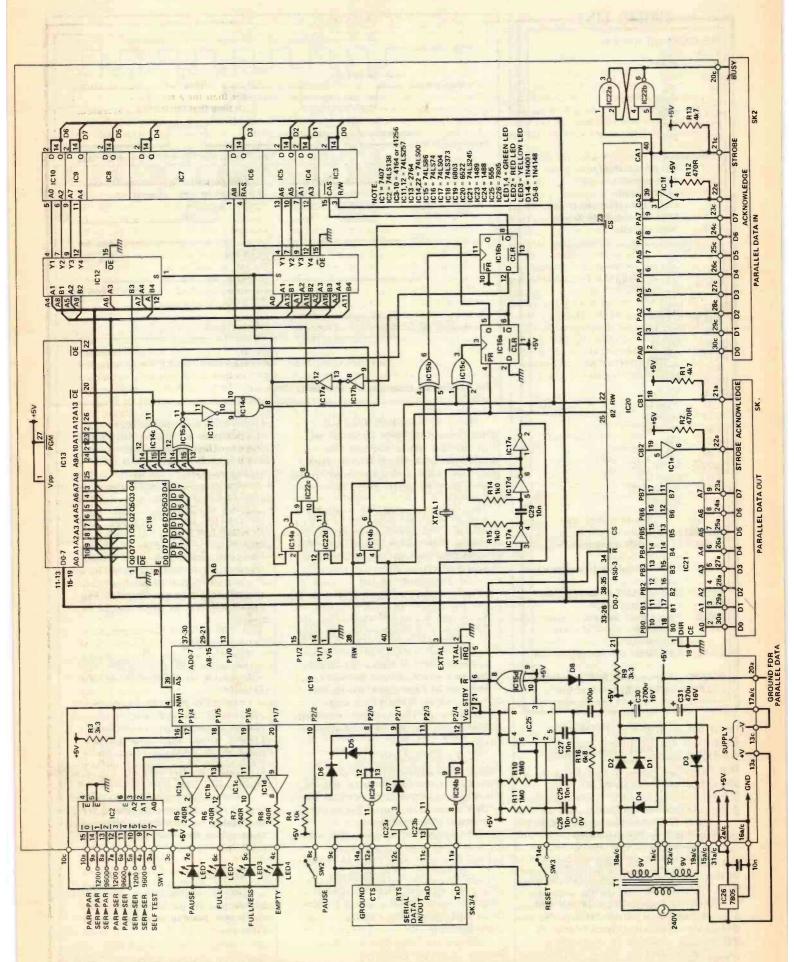

In order to fit I/O lines onto the 6803 CPU without departing from a 40 pin package, the low order address bus and data bus have been multiplexed. As a consequence each memory access cycle is split in two. During the first half, when the Data Strobe (E) is low, the low order address is placed on the multiplexed bus. The falling edge of the Address Strobe (AS) is provided to latch the data into a transparent latch (ICI8).

Internal RAM

The non-multiplexed upper address lines and signals such as Read/Write are also stable by this time. The data to be read or written is transferred during the second part of the cycle, when E is high. It is important that the data buffers in peripheral devices are not activated until E is asserted otherwise bus contention will occur.

To keep the DRAM chips as small and cheap as possible, their address lines are multiplexed. Two strobes, Row Address Strobe (RAS) and Column Address Strobe (CAS) are used to latch each half of the address.

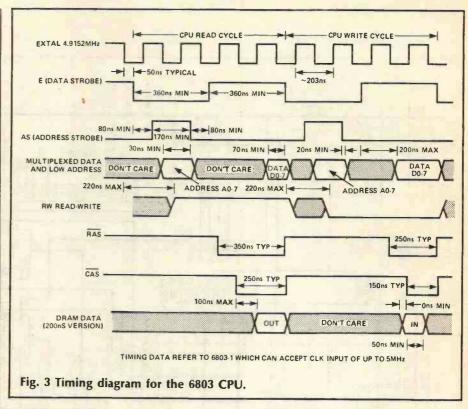

The strobes are so named because each DRAM chip has its memory cells arranged as a square matrix of n rows and n columns, where n is 256 for 64K chips and 512 for 256K chips. Strict timings between these signals and the periods of valid data must be adhered to in order to achieve correct operation. See Fig. 3.

The time delay from E rising to RAS falling is different for read and write cycles. During a read cycle, data from the DRAM must be set up in time for it to be accepted by the 6803 and during a write cycle, the DRAM must wait until data from the 6803 is valid before accepting it. The input clock to the 6803, which is divided by four to produce E, is used with a dual D type latch K16 to generate the different RAS/CAS timings. No data has been published by the manufacturers as to the relationship betwen the clock input and the data strobe E. However, tests on several devices show that there is typically a 50ns delay from the falling edge of the clock to a transition of E.

The Read/Write signal is used to modify the time when the IC16 latches are clocked. This is done with an exclusive-OR gate. When reading, the RAS signal is sent low on the first clock transition after E is high — this is the low to high edge. The low half of the address is latched into the DRAM at this point. Two logic gate delays provide the interval between RAS going low and the select signal of the 74LS257 multiplexers changing, so that the other half of the address is ready for when CAS goes low.

On the next clock transition of the same phase, if the correct address is decoded then CAS is sent low. Sufficient time is allowed for the data to be read by the CPU — which latches it on the falling edge of E. RAS and CAS are sent high again when E goes low and thus completes the read cycle.

During the write cycle, the same process as above occurs, but the Read/Write line now makes IC16 clock on the high to low edge of the input clock. This delays the production of RAS and CAS by half a clock period (about 100ns), ensuring the data from the CPU is valid by the time that it is latched into the DRAM by the falling edge of CAS.

Since the period of E is fixed, the active part of a DRAM write cycle is 100ns shorter than for a read cycle.

Each time that the DRAM is accessed, all the locations in the column of the row that is addressed are refreshed. To refresh the whole chip, every row must be accessed at intervals of not more than 4ms.

A background program accesses every row once in 4ms. Timed interrupts trigger a program that runs through 256 consecutive bytes of EPROM. By arranging the low order address to be latched by RAS and strobing RAS on every memory access cycle even if the DRAM is not being accessed, the program in EPROM will keep the memory refreshed. A loss of just 5% processing speed results.

#### Interfaces

The centronics interfaces are connected to a 6522 Versatile Interface Adapator IC20. Port B is used for parallel data output and Port A for parallel data input. Each centronics interface has three handshake lines. When the data has been set up and is stable, the sending unit pulses the STORE line low for a minimum of 0.5µs. The BUSY line is then sent high by the receiving device until it is ready to accept more.

At this point the ACKNOWLEDGE line is given a low pulse by the receiving unit to indicate that the current transfer is complete. The 6522's handshake lines are set to act as STROBE and ACKNOWLEDGE signals for each port although an additional RS flip-flop is required to generate the BUSY signal.

Parallel output data is buffered by a K21 and the handshake lines are buffered using spare gates from ICI. This enables long cables (over 3m) to be used.

The 6803's Serial Communications Interface is programmed to operate in the standard mark/space format with one start bit, one stop bit and no parity. The clock source is derived from the processor clock. A 4.9152MHz crystal must be used to generate the common baud rates of 1200 and 9600.

Consequently, the processor clock is 1.23MHz which requires a 1.25MHz version of the 6803, or better, and a 1.5MHz version of the 6522. It is unlikely a 1MHz 6803 and 6522 will fail to operate under these conditions.

The RTS and CTS handshaking lines are used with no facility for XON/XOFF handshaking. So, a full duplex interface can be split in two, one half to receive data only from the computer and the other to send data only to the printer. This enables serial-serial data transfers to take place concurrently without plug changing. If serial-serial transfers will never be used in a particular application, there is little point in using two D-type connectors.

&80-FF

Fig. 2 The circuit diagram of the printer buffer.

used for all the ICs. However, note that all the holes must be soldered both sides to connect the two PCB foils. In any case a socket should be used for the EPROM (IC13) in case a modified program is ever required.

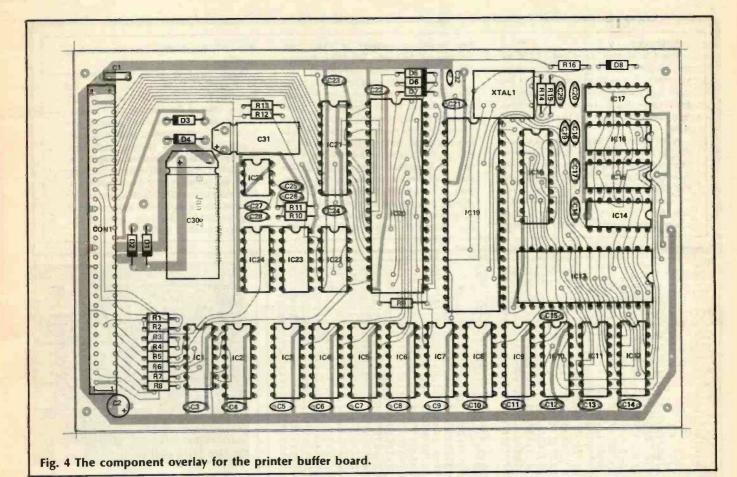

Figure 5 shows the component overlay for the PCB. Before soldering in the DIN 41612 connector, it should be properly seated on the PCB and then fixed to it with 2.5x10mm bolts.

To ensure that the case of the crystal does not short circuit the tracks on the component side of the board, a piece of insulating material should be fixed to the downward facing side.

The freshly soldered PCB should be carefully cleaned of flux on the underside of the board using a small brush and paraffin, with a finer solvent used afterwards to wash away the paraffin.

Finally, insert the ICs. Avoid wearing man-made clothes so as to keep static to a minimum and always rest ICs on a conducting surface such as the non-painted side of a biscuit tin lid.

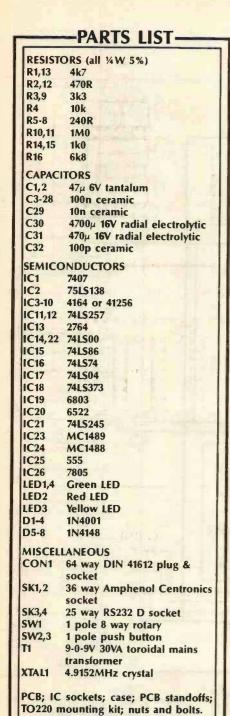

Either 4164 or 41256 ICs may be used for IC3-10 to give a buffer size of 64K or 256K. The correct first byte of the EPROM software for the buffer size must be used.

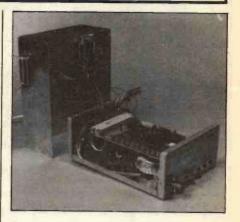

The printer buffer has been designed to fit into a pressed sheet metal box approximately 160mm wide, 80mm tall and 200mm long. The voltage regulator (IC26) bolts to the side of the case.

In the prototype the Centronics connectors are mounted on each side of the box, the RS232 connectors on the back with the switches and LEDs on the front. All connections to off-board components are made via a 64 way DIN 41612 connector located at one end (Fig. 6). Three support locations have been provided on the PCB so that it can be fixed to the base of the box, straddling the mains transformer.

Before drilling any holes, satisfy yourself that the components will all fit together in their intended positions.

Remember to allow enough space for the DIN connector to be removed from the PCB with all the wires attached to it.

For greatest safety, the earth of the mains cable should be bolted directly to the base of the case using a spade terminal. If the signal ground potential of any of the units likely to be connected to the buffer is not floating or Earth, then the 7805 regulator must be insulated from the case using standard TO220 insulating washers.

## Software

Finally, a programmed EPROM should be plugged into position as ICI3.

The EPROM can be either a 2764 or 27128 type and it should be programmed according to Listing 1. For use with a 64K buffer the first byte should contain the number 06. For a 256K buffer the first byte should be 00.

This arrangement also allows a 64K buffer to be upgraded to 256K by replacing the RAM chips and over-programming the first byte with 00.

**Testing**

Before using the unit a series of checks must be made. Run through the connections to the DIN plug and make sure that all are correct. Take particular care with the supply wires from the transformer. Turn the unit on

# PROJECT: Printer Buffer

| Pin Pin 1 2 3 4 5                                                                  | Row a Row a ground +5V mode 7 select mode 6 select mode 5 select                                                                                                                                                       | Row b<br>Row b<br>ground<br>+5V<br>LED anodes<br>EMPTY LED cathode<br>FULLNESS LED                                                                                                                                                | 29<br>30<br>31<br>32 | D1 (OUT) DO (OUT) +5V transformer ground Table 1 DIN 41612 co |                                                                                             | D1 (IN) DO (IN) +5V transformer ground onnector pin-out. |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20 | mode 4 select mode 3 select mode 2 select mode 1 select mode 0 select TxD CTS IC24 +V RS232 ground +V rectified output 7805 regulator ground -V rectified output T1 secondary I T1 secondary II Centronics data ground | cathode FULL LED cathode PAUSE LED cathode PAUSE switch PAUSE/RESET common mode select return RxD RTS IC24 -V RESET switch +V rectified output 7805 regulator ground -V rectified output T1 secondary I T1 secondary II BUSY (IN) |                      | 19-28<br>29-36                                                | Function Strobe D0 D1 D2 D3 D4 D5 D6 D7 Acknowledge Busy Not connected Ground Not connected |                                                          |

| 21<br>22<br>23<br>24<br>25<br>26<br>27<br>28                                       | ACKNOWLEDGE (OUT) STROBE (OUT) D7 (OUT) D6 (OUT) D5 (OUT) D4 (OUT) D3 (OUT) D2 (OUT)                                                                                                                                   | ACKNOWLEDGE (IN)  STROBE (IN)  D7 (IN)  D6 (IN)  D5 (IN)  D4 (IN)  D3 (IN)  D2 (IN)                                                                                                                                               |                      | Pin 2 3 4 5 7                                                 | Function TxD RxD RTS CTS Ground Table 3 RS232 into                                          | erface connections.                                      |

# **PROJECT: Printer Buffer**

Software

The 128 bytes of zero page RAM are used both for the stack and program variables. The main requirement of the stack is to store registers during a refresh interrupt — using seven bytes at a time. This leaves the entire DRAM free to hold

After the buffer has been reset it must decide which operating mode it is in. In order to save components, the CPU I/O lines connected to the LED outputs also drive the mode select decoder (IC2). The decoder is enabled and each output is selected in turn until the return connection causes an NMI interrupt.

The selected output at that time determines the mode. The I/O lines then revert to their normal operation.

The main buffer program selected by the mode switch consists of a never ending loop. If the buffer has spare capacity, the input source is checked and if more data is ready it is read and put into the buffer. In the case of serial input, if there are less than 64 bytes free then the CTS handshake line is negated. The loop then checks the status of the output port. If there is data in the buffer and the printer is ready to accept it (either by acknowledging the previous byte sent to the Centronics output or asserting the RTS serial handshake line) the next byte

Again, for serial inputs, the CTS output asserted if there are over 128 bytes free in the buffer. A branch back to the start of the loop is then made.

This alternate sampling ensures the printer is kept supplied with data even if the computer is sending data very rapidly. When receiving serial input, any characters that result from a framing error are ignored. It is less annoying to find a character missing in a pice of text than to have a corrupted character ruin a printout by changing one of the printer's internal settings.

## BUYLINES

The printer buffer uses components which are for the most part easily obtainable from usual suppliers. The case used for the prototype is available from Maplin (part no. XB71N). The 6803 can be bought from Midwich (Tel: (0379)

The PCB is available from the ETI PCB Service see the back of this issue for details.

The author can supply the source code (£7.50) or the source code and a 6803 assembler (£15) copied onto formatted BBC micro disks supplied by readers.

Programmed EPROMs are available for £6 (reader's 2764 or 27128 EPROM) or £9 (EPROM supplied). Please specify whether the 64K or 256K version is

The author will also build and test boards purchased from the PCB service for £70. This includes all on-board components but not the case, switches, connectors and so forth. Please address all enquiries and orders to Leycester Whewell, St. Just, Berrington Road, Tenbury Wells, WR15 8EJ.

without the PCB plugged in and check that each of the supply inputs read 9V relative to ground and that they are at 18V relative to each other.

Plug in the PCB and run the unit in the self test mode. The memory test involves writing to every byte of RAM, waiting 10ms to check the refresh system and

then verifying that data. If successful, the EMPTY LED is toggled and next time the process is repeated with a different arrangement of data. A full check on 256K of RAM takes a couple of seconds.

To check the parallel ports, a lead with a Centronics connector at each end is required. By connecting the output to the input, a check is made on the transfer of 256 bytes of data. When the data is verified and separate tests on the handshake lines are satisfactory then the

FULL LED is toggled.

The serial interface is checked in a similar way - by connecting the data lines and the handshake lines together. Tests are performed at 1200 and 9600 baud and if successful, the FULLNESS LED is toggled. If all is well, the buffer is now ready to earn its keep.

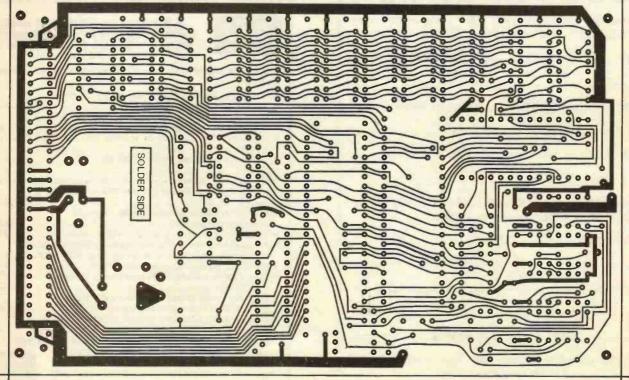

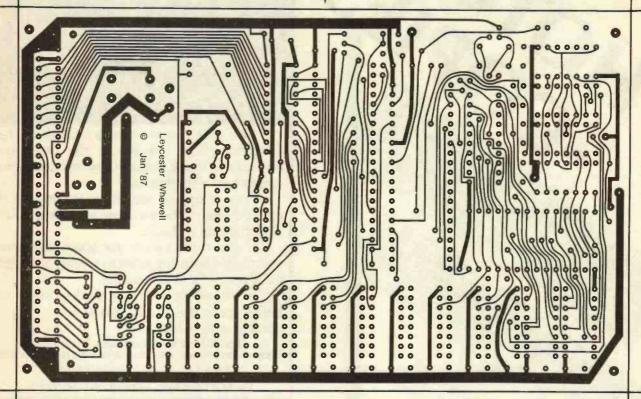

The Printer Buffer topside foil.

The Printer Buffer solderside foil.